Mail:info@anke-pcb.com

WhatApp/WeChat: 008618589033832

Skype: sannyduanbsp

Tre aspetti per garantire l'integrità del potere inProgettazione di PCB

Nel design elettronico moderno, l'integrità dell'alimentazione è una parte indispensabile del design del PCB. Per garantire il funzionamento stabile e le prestazioni dei dispositivi elettronici, dobbiamo considerare e progettare in modo completo dalla fonte di alimentazione al ricevitore.

Attraverso la progettazione e l'ottimizzazione attentamente dei moduli di potenza, i piani di strati interni e i chip di alimentazione possono davvero raggiungere l'integrità di potenza. Questo articolo approfondirà questi tre aspetti chiave per fornire una guida pratica e strategie per i progettisti di PCB.

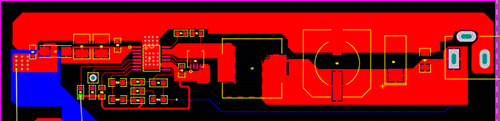

I. Cablaggio del layout del modulo di alimentazione

Il modulo di alimentazione è la fonte di energia di ogni dispositivo elettronico, le sue prestazioni e il layout influenzano direttamente la stabilità e l'efficienza dell'intero sistema. Il layout e il routing corretti possono non solo ridurre l'interferenza del rumore, ma anche garantire un flusso di corrente regolare, migliorando così le prestazioni complessive.

2. Layout del modulo di forza

1. Elaborazione della Source:

Il modulo di potenza dovrebbe essere prestato particolare attenzione poiché funge da punto di partenza della potenza. Per ridurre l'introduzione del rumore, l'ambiente attorno al modulo di potenza dovrebbe essere mantenuto il più pulito possibile per evitare l'adiacenza ad altrialta frequenzao componenti sensibili al rumore.

2. Close al chip di alimentazione:

Il modulo di potenza deve essere posizionato il più vicino possibile al chip fornito dalla potenza. Ciò può ridurre le perdite nell'attuale processo di trasmissione e ridurre i requisiti dell'area del piano di strato interno.

3. Considerazioni sulla dissipazione del calo:

Il modulo di alimentazione può generare calore durante il funzionamento, quindi dovrebbe essere assicurato che non vi siano ostacoli sopra per la dissipazione del calore. Se necessario, i dissipatori di calore o le ventole possono essere aggiunti per il raffreddamento.

4. Evitare i loop:

Durante il routing, evitare di formare anelli di corrente per ridurre la possibilità di interferenza elettromagnetica.

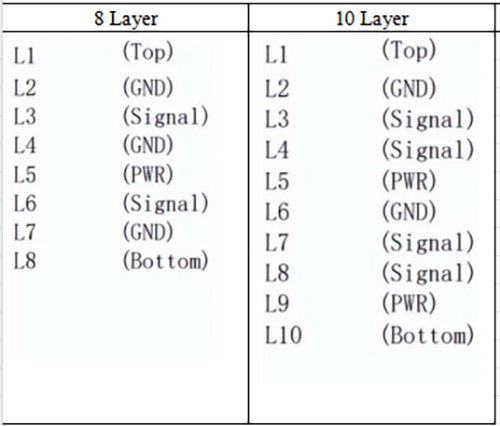

Ii. Pianificazione della progettazione del piano di strato interno

A. Design dello stack di livello

In PCB EMC Design, Layer Stack Design è un elemento chiave che deve considerare il routing e la distribuzione dell'alimentazione.

UN. Per garantire le caratteristiche di bassa impedenza del piano di potenza e assorbire l'accoppiamento del rumore del terreno, la distanza tra potenza e piano di terra non deve superare i 10 milioni, in genere consigliato per essere inferiore a 5 mil.

B. Se non è possibile implementare un singolo piano di potenza, è possibile utilizzare uno strato superficiale per disporre il piano di alimentazione. La potenza e i piani di terra strettamente adiacenti formano un condensatore piano con una minima impedenza CA e eccellenti caratteristiche ad alta frequenza.

C. Evita due strati di potenza adiacenti, in particolare con grandi differenze di tensione, per prevenire l'accoppiamento del rumore. Se inevitabile, aumenta il più possibile la spaziatura tra i due strati di potenza.

D. I piani di riferimento, in particolare i piani di riferimento di potenza, dovrebbero mantenere caratteristiche di bassa impedenza e possono essere ottimizzati attraverso i condensatori di bypass e le regolazioni del livello.

B. Segmentazione del potere multiplo

UN. Per specifiche sorgenti di alimentazione a piccolo raggio, come la tensione di lavoro del nucleo di un determinato chip IC, il rame dovrebbe essere posata sullo strato di segnale per garantire l'integrità del piano di potenza, ma evitare di posare il rame di potenza sullo strato superficiale per ridurre le radiazioni del rumore.

B. La selezione della larghezza di segmentazione dovrebbe essere appropriata. Quando la tensione è maggiore di 12 V, la larghezza può essere 20-30 mil; Altrimenti, scegli 12-20 mil. La larghezza di segmentazione tra fonti di potenza analogica e digitale deve essere aumentata per evitare che la potenza digitale interferisca con la potenza analogica.

C. Le reti di alimentazione semplici dovrebbero essere completate sul livello di routing e le reti di alimentazione più lunghe dovrebbero avere i condensatori di filtro aggiunti.

D. Il piano di potenza segmentato deve essere mantenuto regolare per evitare forme irregolari causando risonanza e aumento dell'impedenza di potenza. Non sono consentite strisce lunghe e strette e divisioni a forma di manubrio.

Filtraggio di C.Plane

UN. Il piano di potenza deve essere strettamente accoppiato con il piano di terra.

B. Per i chip con frequenze operative superiori a 500 MHz, si basano principalmente sul filtraggio dei condensatori del piano e utilizzano una combinazione di filtraggio dei condensatori. L'effetto di filtraggio deve essere confermato dalla simulazione di integrità della potenza.

C. Installare gli induttori per i condensatori di disaccoppiamento sul piano di controllo, come ampliamento dei cavi di condensatore e aumentare la VIA del condensatore, per garantire che l'impedenza di potenza sia inferiore all'impedenza target.

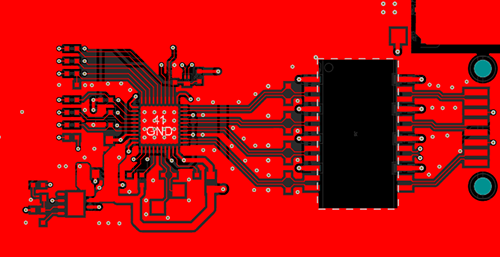

Iii. Cablaggio del layout con chip di potenza

Il chip di potenza è il nucleo dei dispositivi elettronici e garantire la sua integrità di potenza è fondamentale per migliorare le prestazioni e la stabilità del dispositivo. Il controllo dell'integrità della potenza per i chip di potenza comporta principalmente la gestione del routing dei perni di potenza del chip e la corretta layout e il cablaggio dei condensatori di disaccoppiamento. Quanto segue in dettaglio in dettaglio e consigli pratici su questi aspetti.

A.CHIP IL PROPRIETTO PIN ALTENZA

Il routing dei pin di potenza di chip è una parte cruciale del controllo dell'integrità della potenza. Per fornire una fornitura di corrente stabile, si consiglia di ispessire il routing dei perni di potenza, generalmente alla stessa larghezza dei perni del chip. In genere, illarghezza minimanon dovrebbe essere inferiore a 8mil, ma per risultati migliori, cerca di ottenere una larghezza di 10 milioni. Aumentando la larghezza del routing, l'impedenza può essere ridotta, riducendo così il rumore di potenza e garantendo un sufficiente alimentazione di corrente al chip.

B.Layout e routing di condensatori di disaccoppiamento

I condensatori di disaccoppiamento svolgono un ruolo significativo nel controllo dell'integrità della potenza per i chip di potenza. A seconda delle caratteristiche dei condensatori e dei requisiti di applicazione, i condensatori di disaccoppiamento sono generalmente divisi in grandi e piccoli condensatori.

UN. Capacità di grandi dimensioni: i grandi condensatori sono generalmente distribuiti uniformemente attorno al chip. A causa della loro frequenza di risonanza inferiore e del raggio di filtraggio più ampio, possono effettivamente filtrare il rumore a bassa frequenza e fornire un alimentatore stabile.

B. Piccoli condensatori: i piccoli condensatori hanno una frequenza di risonanza più elevata e un raggio di filtraggio più piccolo, quindi dovrebbero essere posizionati il più vicino possibile ai perni del chip. Posizionarli troppo lontano potrebbe non filtrare efficacemente il rumore ad alta frequenza, perdendo l'effetto di disaccoppiamento. Il layout corretto garantisce che l'efficacia dei piccoli condensatori nel filtraggio del rumore ad alta frequenza sia completamente utilizzata.

C. Metodo di cablaggio dei condensatori di disaccoppiamento parallelo

Per migliorare ulteriormente l'integrità della potenza, i condensatori di disaccoppiamento multipli sono spesso collegati in parallelo. Lo scopo principale di questa pratica è ridurre la serie equivalente induttanza (ESL) dei singoli condensatori attraverso una connessione parallela.

Quando si parallela a più condensatori di disaccoppiamento, è necessario prestare attenzione al posizionamento di VIA per i condensatori. Una pratica comune è quella di compensare le VIA del potere e del terreno. Lo scopo principale di ciò è ridurre l'induttanza reciproca tra i condensatori di disaccoppiamento. Assicurarsi che l'induttanza reciproca sia molto più piccola dell'ESL di un singolo condensatore, in modo che l'impedenza ESL complessiva dopo aver parallelo a più condensatori di disaccoppiamento sia 1/n. Riducendo l'induttanza reciproca, l'efficienza di filtraggio può essere efficacemente migliorata, garantendo una migliore stabilità di potenza.

Disposizionee il routing dei moduli di alimentazione, la pianificazione del design del piano di strato interno e la corretta gestione del layout e dei cablaggi del chip di potenza sono indispensabili nella progettazione di dispositivi elettronici. Attraverso il layout e il routing adeguati, possiamo garantire la stabilità e l'efficienza dei moduli di potenza, ridurre le interferenze del rumore e migliorare le prestazioni complessive. La progettazione dello stack di livello e la segmentazione di potenza multipla ottimizzano ulteriormente le caratteristiche dei piani di alimentazione, riducendo l'interferenza del rumore di potenza. La corretta gestione del layout del chip di potenza e dei cablaggi e dei condensatori di disaccoppiamento sono cruciali per il controllo dell'integrità della potenza, garantendo una fornitura di corrente stabile e un filtro efficace del rumore, migliorando le prestazioni e la stabilità del dispositivo.

Nel lavoro pratico, vari fattori come la grandezza corrente, la larghezza del routing, il numero di VIA, gli effetti di accoppiamento, ecc., Devono essere considerati in modo completo per prendere decisioni razionali e di routing. Seguire le specifiche di progettazione e le migliori pratiche per garantire il controllo e l'ottimizzazione dell'integrità di potenza. Solo in questo modo possiamo fornire un alimentazione stabile ed efficiente per i dispositivi elettronici, soddisfare le crescenti richieste di prestazioni e guidare lo sviluppo e il progresso della tecnologia elettronica.

Shenzhen Anke PCB Co., Ltd

Post Time: mar-25-2024